2024.3Q 분기별 매출액 성장 2024.3Q 분기별 영업이익 성장 2024.3Q 분기별 수주잔고 성장 2024.3Q 8주에 80%이상 상승 2024.3Q 신저가대비 100%이상 상승 2024.3Q 50일신고가+신저가대비 70%이상 2024.3Q 2주에 15%이상 하락

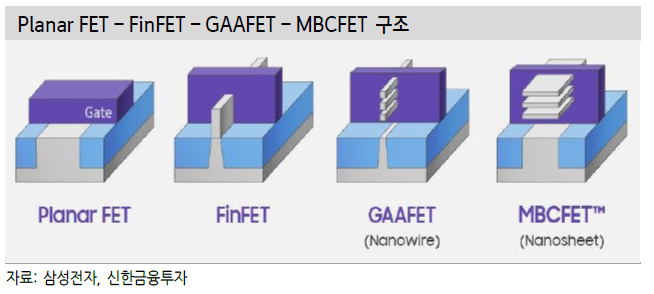

반도체 핵심 소자인 Transistor를 구현할 때, Foundry 전공정에 요구되는 것은 처리 속도를 증가시키고, 소비전략을 감소시키는 것이다. Transistor의 선폭이 좁아지면, 누설전류(Leakage Current)가 발생하여 Short Channel Effect가 발생한다. 누설전류가 발생할 경우, 전력소모량이 많아진다. 현재까지 Foundry 업체들은 HKMG(High-k Metal Gate)와 FinFET 공정을 적용하여 기술을 개발해 왔다.14nm 선폭부터 적용되어 온 FinFET 공정이 4nm 미만 선폭에서는 한계를 보일 가능성이 높다.

그래서 Foundry 업체들은 GAA(Gate All Around) 공정을 적용할 전망이다. 언론 보도에 의하면, 삼성전자는 3nm 선폭부터, TSMC는 3nm 또는 2nm부터 GAA공정을 적용할 계획이다.

GAA를 적용하는 이유는 FinFET과 동일하다. 두 공정 모두 Transistor의 전류가 이동하는 소스와 드레인 사이에 구조를 개선하여 접촉 면적을 늘리고(속도를 증가시키고), 물고기 지느러미 모양처럼 쥐어짜게 만들어 누설전류를 최소화하는 접근이다. GAA는 FinFET보다 전류가 이동하는 접촉 면적이 넓고 전류가 흐르는 채널 4면을 Gate가 둘러싸고 있다. FinFET보다 채널 조정 능력을 추가적으로 개선시킨 방법이다.

GAA는 Transistor 구조를 전면적으로 변경하는 것이기 때문에, 공정 기술상 많은 어려움이 등장할 것으로 전망된다. 구조 변화로 인해 Vth(Threshold Voltage)등 Transistor Engineering이 매우 어려워 진다. 최적의 Transistor 조건을 찾기 위해 상당한 연구 개발 기간이 필요하다. 또한 소스 및 드레인 영역에 pit 또는 hole이 발생할 가능성이 높고, Dry Etch시 PR(Photo Resist)이 마스크 역할을 제대로 수행하기 어려워 Patterning 난이도가 상승할 것이다