전체

반도체

반도체소재부품

반도체장비

차/전력반도체

후공정/기판

2차전지

2차전지소재

2차전지장비

폐배터리

자동차

자동차부품

디스플레이

전기전자

수소

신재생에너지

원자력

에너지/원자재

5G/통신

자율주행

AI/AR/VR

로봇

항공/우주/방위

UAM

철강

비철금속

화장품/유통

여행/카지노

음식료

의류신발

폐기물

플라스틱

미용/의료기기

조선/해운

인터넷/보안

게임

엔터/미디어

정유/화학

건설

기계/유틸

투자관련

경제/통계

기타

2025.4Q 분기별 매출액 성장 2025.4Q 분기별 영업이익 성장 2025.4Q 분기별 수주잔고 성장 2025.4Q 8주에 80%이상 상승 2025.4Q 신저가대비 100%이상 상승 2025.4Q 50일신고가+신저가대비 70%이상 2025.4Q 2주에 15%이상 하락 2025.4Q 반등강도(30~40)

2025.4Q 분기별 매출액 성장 2025.4Q 분기별 영업이익 성장 2025.4Q 분기별 수주잔고 성장 2025.4Q 8주에 80%이상 상승 2025.4Q 신저가대비 100%이상 상승 2025.4Q 50일신고가+신저가대비 70%이상 2025.4Q 2주에 15%이상 하락 2025.4Q 반등강도(30~40)

2023.10.16

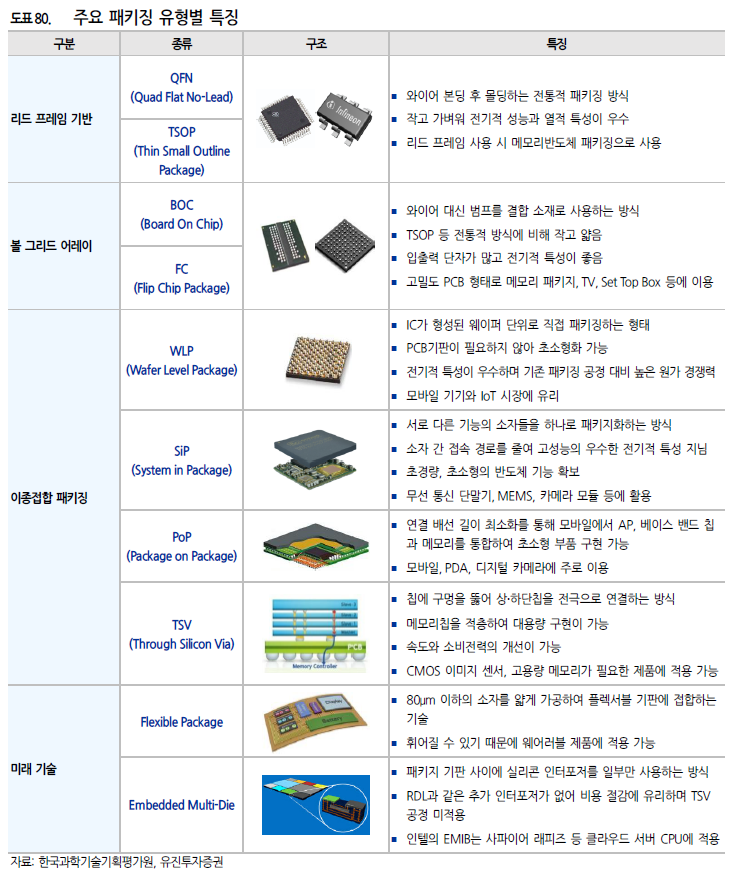

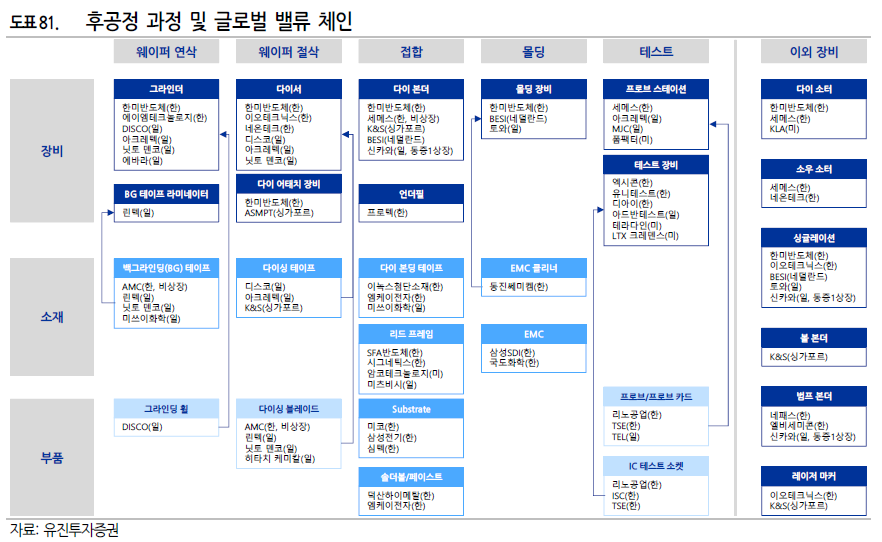

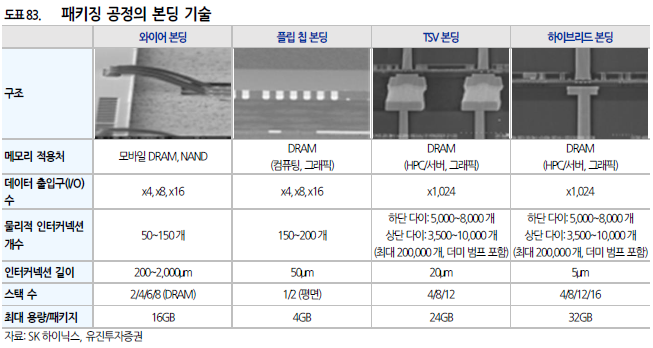

패키징 유형별 특징 / 패키징 공정의 본딩 기술

[유진투자증권 임소정] 소부장 레시피

패키징은 더 이상 단순히 칩을 잘라 포장하여 기판에 얼기설기 배선을 연결하는 공정이 아니다. 점점 작아지는 칩과 기판의 연결, 서로 다른 칩과 칩 간의 연결, 그리고 이를 모두 조밀하게 집적하는 고밀도 인터커넥션이 패키징 공정의 핵심이 되었다고 할 수 있다. 특히 서로 다른 크기와 기능을 가진 칩들을 하나의 패키지로 제작해 단일 제품처럼 작동하는 이종 접합 기술의 발전이 두드러진다. 과거에는 소자의 종류가 CPU 와 메모리 정도로 적었지만, 모바일과 웨어러블 시장 등이 커지면서 공간적 제약을 이겨내기 위한 방식으로 SoC(System on Chip)이 소개되었다.

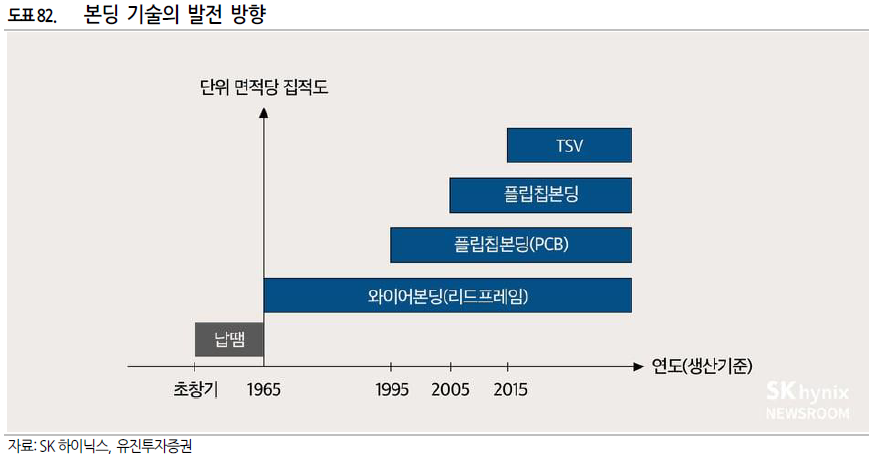

전공정 기술을 활용하여 한 칩에 집적하고 배선하는 방식이다보니, 다이 크기가 커지면서 웨이퍼 수율은 떨어지고 불량률은 상승했다. 또한 SoC 방식을 사용하면 가장 첨단의 공정을 이용해 모든 칩을 만들어야하기 때문에 비용 면에서도 불리했다. 이에 떠오른 대안이 바로 칩렛(Chiplet) 기술이다. 기존 칩에서 필요한 기능을 각각 분리하여 작은 칩으로 따로 제조한 뒤에 하나로 합치는 이종 집적 방식이다. 선택과 집중을 통한 개발이 가능하고, 주문 제작식에 용이하여 이미 AMD 의 서버용 GPU 와 삼성전자의 I-Cube 4 등의 제품에 적용되었다. 이 칩렛 방식에서 현재 활발히 사용되는 본딩 방식이 바로 TSV 본딩이고, 기업들은 하이브리드 본딩 상용화를 위한 연구·개발을 진행하고 있다.

후공정/기판 목록