2025.4Q 분기별 매출액 성장 2025.4Q 분기별 영업이익 성장 2025.4Q 분기별 수주잔고 성장 2025.4Q 8주에 80%이상 상승 2025.4Q 신저가대비 100%이상 상승 2025.4Q 50일신고가+신저가대비 70%이상 2025.4Q 2주에 15%이상 하락 2025.4Q 반등강도(30~40)

<트랜지스터>

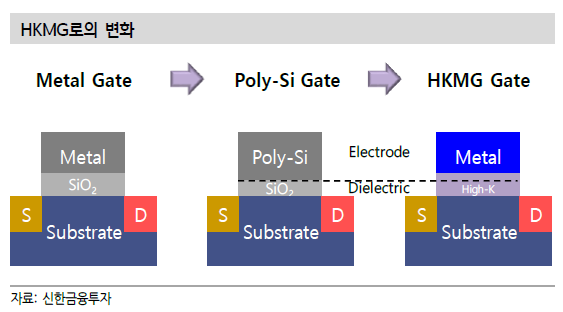

트랜지스터는 동작 방식에 따라 전류 이용 방식(BJT), 전압 이용 방식(FET)으로 나뉜다. 현재 사용되고 있는 방식은 FET 구조이다. FET 구조에서 트랜지스터 단자는 게이트, 소스, 드레인으로 구성 되며, 소스와 드레인 사이 연결 통로를 채널(Channel)이라 한다. 전압 이용 방식(FET)에서는 절연을 통해 단자들간의 전자이동을 막는 것이 필요하다. 게이트와 아래 채널간 전자가 이동하지 않도록 해주는 절연막 이 게이트 옥사이드(Gate Oxide)다. 때문에 게이트 옥사이드는 두꺼울수록 절연성이 높아 유리했다.

그러나 공정 미세화 과정에서 트랜지스터 크기, 선폭은 줄어들고, 이에 동반하여 게이트 옥사이드의 두께도 줄 어들게 된다. 두께가 줄어들 때 발생하는 문제점은 절연성이 낮아 진다는 것이다. 두께는 줄이면서 동시에 절연성 을 높이기 위한 방법으로, 유전율(K)이 높은 High-K 물질을 게이트 옥사이드 층에 사용하게 됐다. 이를 HKMG(High-K, Metal Gate)라 부른다. 25nm에 접어들면서 적용 되기 시작했다.

<캐패시터>

캐패시터의 정전용량(Capacitance)은 전자를 담아두는 공간이다. 공정 미세화 과정에서 간섭현상이 심해지고 정전용량을 높여주는 것이 필요하다. 이를 위한 방법은 1) 면적 확대, 2) 거리 축소, 3) 유전상수가 높은 물질 사용 등이 있다. 이중 1)과 2)는 이미 더 이상 진행하기에 구조적으로 한계에 다다랐다. 거리를 좁히면서 면적을 높이기 위해서는 종횡비를 높여야 하는데, 캐패시터의 종횡비는 이미 100에 가까운 수준이다. 결국 소재의 변화를 통해 정전용량을 높일 수밖에 없다. 사용되는 소재도 변화 중이다. 소재별 조합을 통해 좀 더 유전상수 값을 높이고 있다.