2025.4Q 분기별 매출액 성장 2025.4Q 분기별 영업이익 성장 2025.4Q 분기별 수주잔고 성장 2025.4Q 8주에 80%이상 상승 2025.4Q 신저가대비 100%이상 상승 2025.4Q 50일신고가+신저가대비 70%이상 2025.4Q 2주에 15%이상 하락 2025.4Q 반등강도(30~40)

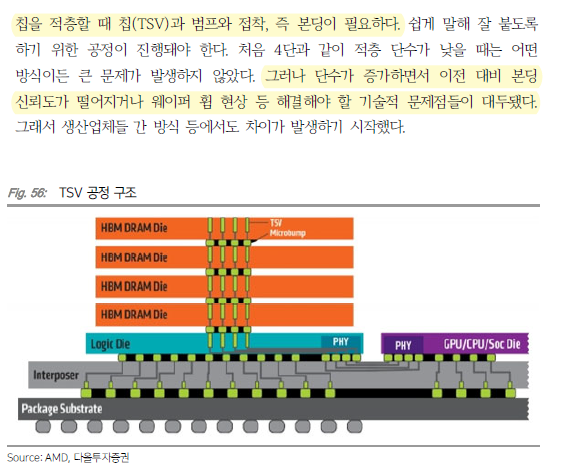

HBM(High Bandwidth Memory) : HBM은 첨단 패키징 관련 기사나 자료에 자주 등장하는 용어이다. 그러나, 아이러니하게도 패키징 기술을 의미하지 않는다. HBM은 사실상 메모리 반도체 중에 고대역폭 그래픽 DRAM을 의미한다. 고대역폭 그래픽 DRAM을 여러 개(8개, 12개, 16개) 모아서 TSV(Through Silicon Via) 방식으로 수직 연결해 데이터 처리 속도를 혁신적으로 끌어올린 고부가가치, 고성능 제품이다. HBM은 1세대(HBM), 2세대(HBM2), 3세대(HBM2E)를 거쳐 현재 4세대(HBM3)까지 개발된 상황이다. SK하이닉스, 삼성전자, Micron 중에서 SK하이닉스의 점유율이 상대적으로 높다.

TSV(Through Silicon Via): HBM이라는 그래픽 DRAM을 패키징하는 과정에서 TSV라는 기술 용어가 약방의 감초처럼 등장한다. TSV는 DRAM 칩에 수천 개의 미세한 구멍을 뚫어 상하층 칩의 구멍을 수직 관통하는 전극으로 연결하는 기술이다. 10년 전에 TSV 기술이 세상에 알려지기 시작했을 때에는 기존의 연결 단자 형성 기술중에 전통적인 와이어 본딩을 대체하는 기술로 알려졌다. 따라서 ‘TSV’라는 용어보다는 ‘TSV 기술을 이용한 본딩’이라는 용어가 좀 더 정확한 표현이다. 기존의 와이어 본딩이 건물의 각 층을 연결하는 계단이나 에스컬레이터라면, TSV는 각 층을 수직으로 관통한다는 의미에서 계단이 애초에 존재하지 않는 건물의 엘리베이터와 비슷하다고 할 수 있다.

에폭시 밀봉재(EMC, Epoxy Molding Compound): EMC라는 용어는 첨단 패키징이 아니라 전통적인 패키징 분야에서도 자주 등장했던 용어이다. EMC는 패키징용 소재를 의미한다. 열경화성 에폭시 고분자 재료와 무기실리카 재료를 혼합한 복합 재료를 기반으로 만들어진 방열 소재이다. 반도체 칩을 밀봉해 열이나 습기, 충격 등 외부 환경으로부터 보호해 주는 역할을 담당한다. 전공정을 마친 후 후공정 단계에서 반도체를 패키징하는 이유는 여러 가지가 존재하는데, EMC와 같은 패키징용 소재로 반도체를 감싸서(덮어서) 보호하는 것도 패키징을 하는 이유 중 하나이다

MR-MUF(Mass Reflow-Molded Under Fill): 앞서 언급된 EMC와 마찬가지로 반도체를 보호하는 과정과 관련된 용어이다. 다만, MR-MUF는 EMC처럼 특정 ‘소재’가 아니라 보호하는 공정의 ‘방식’을 의미한다. 반도체 칩을 쌓아 올린 뒤 칩과 칩 사이 회로를 보호하기 위해 액체 형태의 보호재를 공간 사이에 주입하고, 최하부의 공간(원래는 언더필이 채워지던 공간)까지 모두 채워서 굳히는 방식을 의미한다. SK하이닉스의 발표 자료에 따르면, MR-MUF 방식은 칩을 하나씩 쌓을 때마다 필름형 소재를 깔아주는 방식 대비 공정이 효율적이고, 열 방출에도 효과적인 방식으로 평가받고 있다

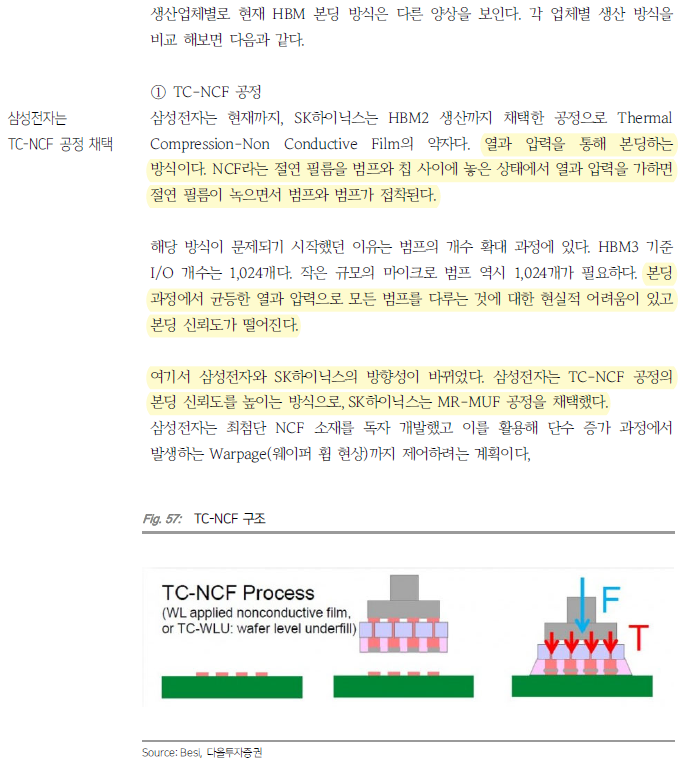

TC NCF(Thermal Compression Non Conductive Film): MR-MUF가 도입되기 전에 적용되던 방식이다. SK하이닉스는 HBM을 패키징할 때 TC NCF를 더 이상 시용하지 않고 MR-MUF 방식을 사용하고 있지만, 삼성전자는 HBM을 패키징할 때 TC NCF 방식을 적용하고 있다. TC NCF 방식이란 칩 사이에 NCF(에폭시와 아크릴소재가 섞인)라는 절연 필름을 덧대고, 열과 압력을 가해 위쪽을 꾹 눌러서 붙이면 마침내 절연 필름이 녹아 접착되는 공정이다. 열과 압력을 가하기 때문에 이를 의미하는 Thermal Compression이라는 용어를 TC로 줄여서 NCF 앞에 붙인다. 그래서 NCF가 아니라 TC NCF라고 불리는 것이다.

범프(Bump): 반도체 칩과 기판을 연결하는 구 형태의 전도성 돌기를 의미한다. 범프를 형성하는 소재에 따라 골드 범프 또는 솔더 범프로 구분된다. 범프 검사 장비 공급사 Camtek에서는 구리 기둥(Copper pillar) 형태의 범프, 크기가 아주 작은 마이크로 범프도 모두 범프의 일종으로 분류한다

RDL(Re-Distribution Layer, 재배선층): 크기가 작은 반도체 회로와 크기가 큰 기판 회로를 전기적으로 연결하기 위해 중간에 새 회로를 구성하는 것을 의미한다. RDL을 형성하기 위해 스퍼터링 공정으로 금속 박막층을 만든다. 그리고 그 위에 두꺼운 포토 레지스트를 도포한다. 이후 포토 공정으로 패턴을 만들고, 패턴으로 열린 부분에 전해 도금으로 금속 물질을 채워 넣어 금속 배선을 형성한다.

칩렛(Chiplet): 칩을 기능별로(컨트롤러, 고속 메모리 등) 쪼개어 별도의 웨이퍼로 제작한 후, 각각의 칩 조각(Chiplet)을 하나의 기판 위에 수평 또는 수직 적층한 뒤 서로 연결하는 기술이다. 최근에 언론에 여러 번 보도된 2.5D 패키징이나 3.0D 패키징은 칩렛 구조의 일종이다. 서로 다른 칩을 수직으로 완벽하게 적층하면 3.0D 패키징이고, 수직 구조와 수평 구조가 혼합되어 있으면 2.5D 패키징이라고 볼 수 있다.

하이브리드 본딩: 동 용어는 ‘하이브리드’라는 단어 때문에 무엇인가 서로 성질이 다른 것들을 겹쳐 놓은 듯한 느낌을 준다. SK하이닉스의 발표 자료에 따르면, ‘하이브리드(Hybrid)’라는 용어는 두 가지 유형의 계면(면과 면사이의)에서 본딩(연결해서 점처럼 이어주는 것)이 동시에 형성되는 것을 나타내기 위해 사용된다. 하나는 산화물 면끼리의 본딩이고, 다른 하나는 구리로 이루어진 면끼리의 본딩이다. 하이브리드 본딩은 다양한 이름으로 불리고 있다. 하이브리드 본딩은 서로 연결되는 공간에 범프(돌기)가 존재하지 않을 수도 있어서 범프리스(Bumpless)공정이라 불리기도 하고, 구리와 구리 면이 서로 바짝 붙는다(접촉한다)는 의미에서 Copper to Copper bonding 공정이라 불리기도 한다. 기존 패키징과 달리 남는 여유 공간이 거의 없어진다는 의미에서 갭리스(Gap-less) 공정 또는 다이렉트 공정이라 불리기도 한다. 상기에 언급된 칩렛 기술 채택이 가속화되기 시작하며 하이브리드 본딩 기술이 주목받고 있으며, AMD가 설계하고 TSMC가 제조한 제품에 하이브리드 본딩 기술이 적용되며 최근에도 많은 관심을 불러 일으키고 있다